TSMC avança para próxima geração de embalagem de chips para Nvidia e Google

A Taiwan Semiconductor Manufacturing Co. está perto de finalizar as especificações de uma nova abordagem para embalagem de chips para atender à demanda por chips de IA mais potentes, com planos de iniciar a produção em pequenos volumes por volta de 2027, apurou a Nikkei Asia. Enquanto os chips são geralmente construídos em wafers redondos […] O post TSMC avança para próxima geração de embalagem de chips para Nvidia e Google apareceu primeiro em O Cafezinho.

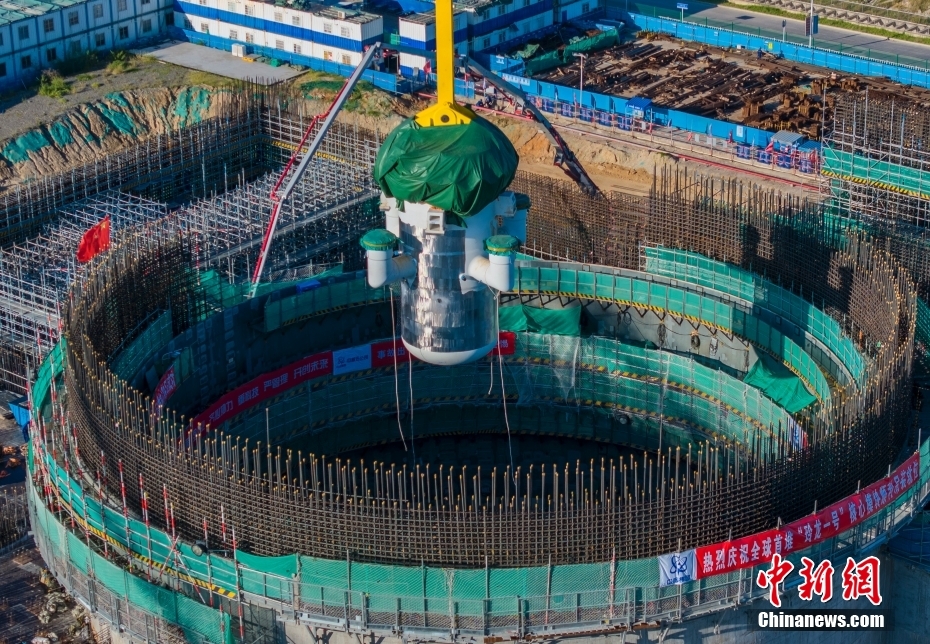

A Taiwan Semiconductor Manufacturing Co. está perto de finalizar as especificações de uma nova abordagem para embalagem de chips para atender à demanda por chips de IA mais potentes, com planos de iniciar a produção em pequenos volumes por volta de 2027, apurou a Nikkei Asia.

Enquanto os chips são geralmente construídos em wafers redondos de 300 milímetros, a nova tecnologia da TSMC, conhecida no setor como embalagem avançada em nível de painel, usará um substrato quadrado que acomoda mais semicondutores, aumentando o desempenho computacional.

Definir os padrões tecnológicos para essa embalagem é essencial para a introdução da tecnologia em toda a indústria, pois toda a cadeia de suprimentos, de fabricantes de equipamentos a fornecedores de materiais, precisará adaptar seus produtos para trabalhar com substratos quadrados.

Duas fontes disseram à Nikkei Asia que a primeira geração da nova embalagem da TSMC usará um substrato de 310 mm por 310 mm. Isso é menor do que o tamanho de 510 por 515 mm testado anteriormente, mas ainda oferece mais área do que um wafer redondo convencional.

“A TSMC quer controlar rigorosamente a qualidade e decidiu começar com um formato quadrado um pouco menor em vez de um maior e mais ambicioso, como nos testes anteriores”, disse uma pessoa familiarizada com o desenvolvimento. “É particularmente desafiador revestir todo o substrato de forma uniforme com produtos químicos.”

A TSMC está acelerando o desenvolvimento. Está construindo uma linha piloto na cidade de Taoyuan e pretende iniciar a produção em pequenos volumes por volta de 2027, segundo fontes.

A decisão da TSMC de adotar um tipo radicalmente diferente de embalagem de chips influenciará os cronogramas de produtos e de P&D de diversos fabricantes de equipamentos. Empresas dos EUA, Japão e Taiwan já trabalham para redesenhar suas ferramentas para lidar com o novo formato.

A fabricante também precisa garantir que o novo formato e tamanho ofereçam espaço suficiente nas bordas para que fabricantes de ferramentas desenvolvam equipamentos de manuseio — como braços robóticos — capazes de pegar e posicionar os substratos com eficácia e segurança. A forma quadrada também reduz a área inutilizada nas bordas do substrato, disseram fontes.

A ASE Technology Holding, maior fornecedora mundial de embalagem e teste de chips, confirmou anteriormente que está construindo uma linha de embalagem em nível de painel com substrato de 600 por 600 mm, mas decidiu construir uma linha piloto adicional em Kaohsiung, Taiwan, usando o mesmo tamanho da TSMC após saber da decisão da líder de mercado.

A embalagem de chips já foi vista como tecnologicamente menos exigente que a produção de chips. No entanto, métodos avançados, como a tecnologia CoWoS da TSMC, tornaram-se tão críticos quanto a fabricação para chips de IA, pois integram GPUs, CPUs e memórias HBM em um único superchip, como o Blackwell da Nvidia. Broadcom, Amazon, Google e AMD também dependem da CoWoS da TSMC para suas necessidades de embalagem.

Com o empacotamento convencional em wafers de 300 mm, é possível acomodar cerca de 16 conjuntos dos superchips B200 da Nvidia, 12 conjuntos do MI355 da AMD e cerca de 25 conjuntos das mais recentes unidades tensor do Google, segundo estimativas do Morgan Stanley e executivos da indústria.

À medida que os projetistas de chips buscam maior desempenho combinando mais chips em um único pacote, a abordagem convencional é vista como insuficiente, levando a TSMC a apostar em uma solução radical. O presidente e CEO C.C. Wei confirmou à Nikkei em meados de 2024 que a empresa estava trabalhando nessa tecnologia, prevendo cerca de três anos para sua introdução.

A TSMC considerou colaborar com fabricantes de displays como a Innolux, afiliada da Foxconn, devido à experiência dessas empresas em materiais quadrados ou retangulares. No entanto, decidiu seguir sozinha ao concluir que os padrões de precisão e habilidades da indústria de displays eram insuficientes para processos de embalagem avançados.

O termo embalagem em nível de painel vem do formato do substrato, que se assemelha mais a um painel retangular do que a um wafer redondo.

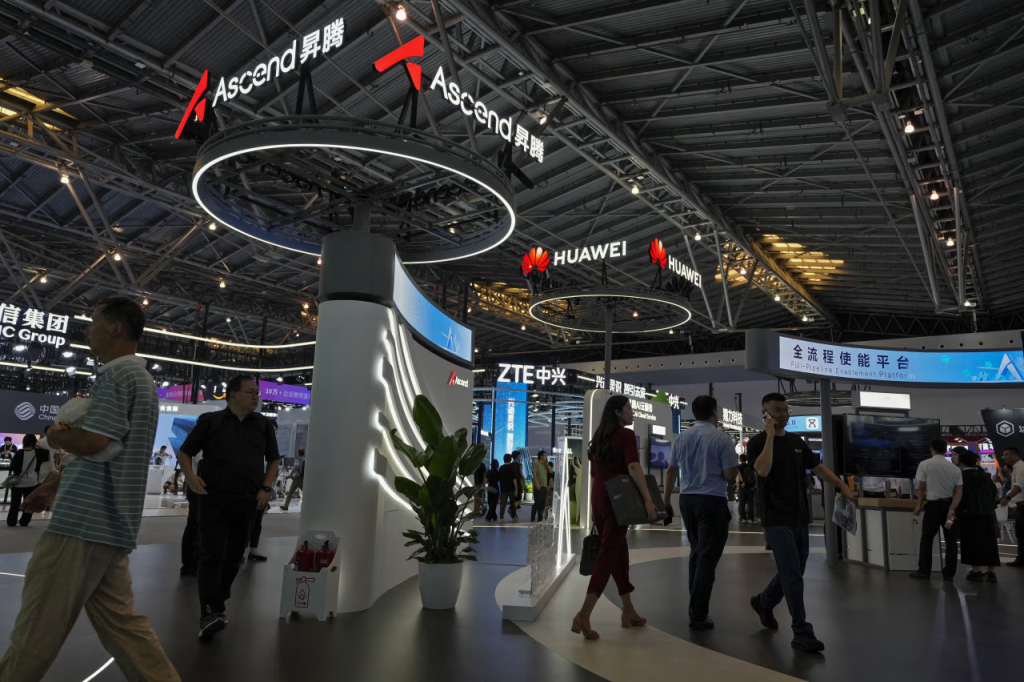

A Huawei Technologies também está empenhada no desenvolvimento da embalagem em nível de painel, enxergando nela uma forma de contornar as restrições dos EUA ao acesso a tecnologias avançadas de fabricação de chips. Seus fornecedores BOE Technology Holding e Tongfu Microelectronics são duas das empresas chinesas que desenvolvem capacidades nesse campo.

Em resposta a pedidos de comentário, a TSMC referiu-se à declaração anterior de Wei confirmando o trabalho nessa tecnologia. A ASE não respondeu aos pedidos de comentário da Nikkei Asia.

Cheng Ting-Fang

Data de publicação: 15 de abril de 2025

Fonte: Nikkei Asia

O post TSMC avança para próxima geração de embalagem de chips para Nvidia e Google apareceu primeiro em O Cafezinho.

.png)

.jpg)

![[Alerta do leitor] Smiles aumentou o preço padrão do seu milheiro de R$ 70 para R$ 80…](https://s0.wp.com/i/blank.jpg)