AMD już korzysta z 2-nanometrowej technologii – to pierwszy przypadek w klasie chipów HPC

AMD ogłasza istotny przełom w technologii 2 nm dla procesora EPYC „Venice”. Firma AMD poinformowała o osiągnięciu ważnego etapu w rozwoju technologii półprzewodników. Procesor nowej generacji AMD EPYC, o nazwie kodowej „Venice”, jest pierwszym produktem HPC (high-performance computing; to zupełnie inna kategoria układów niż procesory mobilne, stosowane m.in. w smartfonach) w branży, który został zaprojektowany... Jeśli artykuł AMD już korzysta z 2-nanometrowej technologii – to pierwszy przypadek w klasie chipów HPC nie wygląda prawidłowo w Twoim czytniku RSS, to zobacz go na iMagazine.

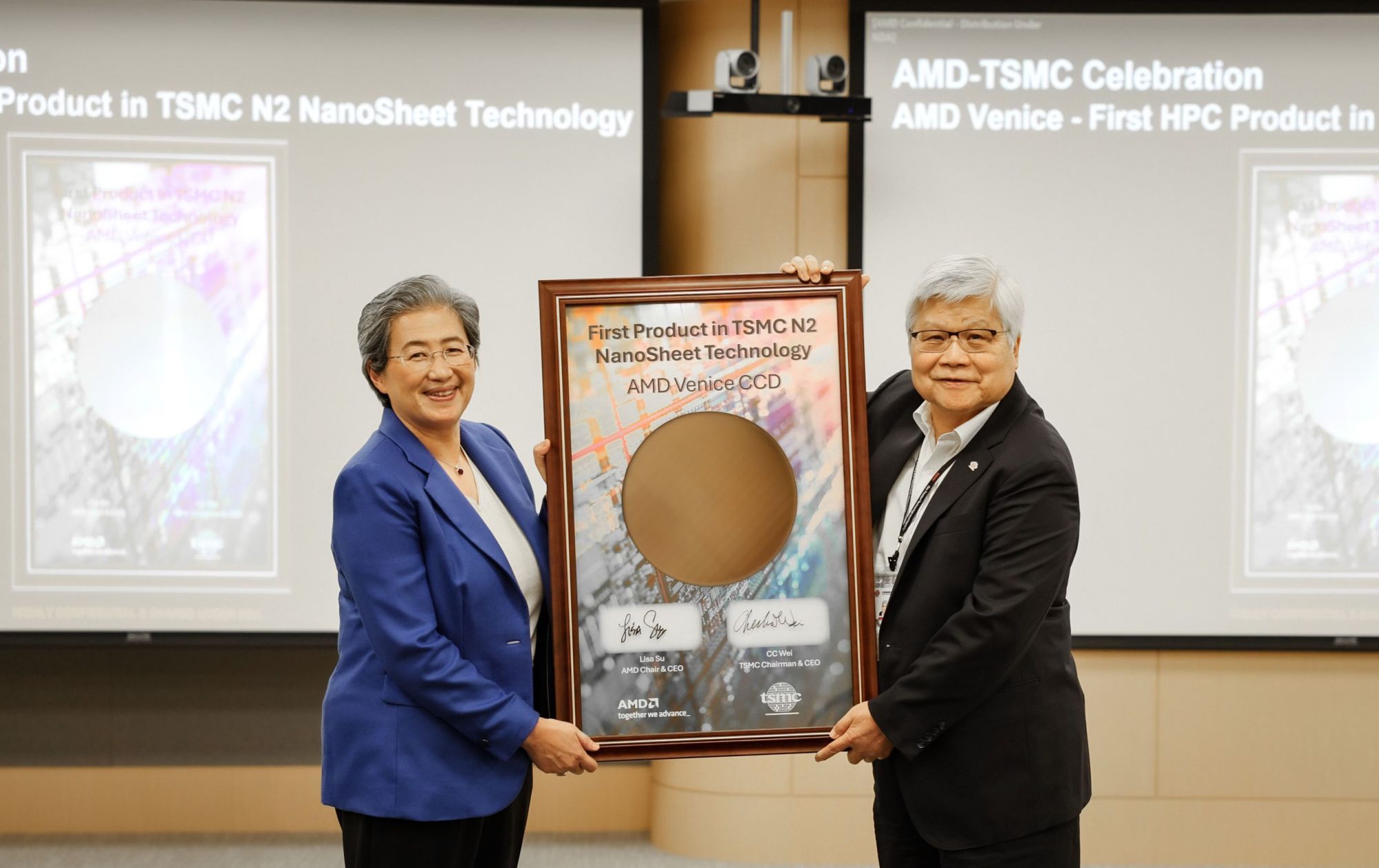

AMD ogłasza istotny przełom w technologii 2 nm dla procesora EPYC „Venice”.

Firma AMD poinformowała o osiągnięciu ważnego etapu w rozwoju technologii półprzewodników. Procesor nowej generacji AMD EPYC, o nazwie kodowej „Venice”, jest pierwszym produktem HPC (high-performance computing; to zupełnie inna kategoria układów niż procesory mobilne, stosowane m.in. w smartfonach) w branży, który został zaprojektowany i uruchomiony w zaawansowanym procesie technologicznym 2 nm (N2) firmy TSMC. To osiągnięcie podkreśla znaczenie współpracy AMD z TSMC w zakresie optymalizacji nowych architektur projektowych z wykorzystaniem najnowszych technologii produkcyjnych.

Procesor „Venice” stanowi kluczowy element realizacji planu rozwoju procesorów AMD dla centrów danych, a jego premiera jest planowana na przyszły rok. Wykorzystanie procesu 2 nm ma na celu poprawę wydajności i efektywności energetycznej w porównaniu z wcześniejszymi generacjami chipów. AMD zaznacza, że jest to pierwszy przypadek zastosowania tej technologii w procesorze przeznaczonym do zastosowań HPC, co może wyznaczyć nowy standard w branży.

AMD napędza przyszłość AI: od centrów danych po kosmos – nowe technologie i przełomowe wyniki

Oprócz sukcesu związanego z procesorem „Venice”, AMD ogłosiło również zakończenie testów i walidacji procesorów 5. generacji AMD EPYC w nowej fabryce TSMC w Arizonie. To potwierdza zaangażowanie firmy w rozwój produkcji półprzewodników na terenie Stanów Zjednoczonych. Oba osiągnięcia są częścią strategii AMD mającej na celu dostarczanie nowoczesnych rozwiązań dla centrów danych.

Szczegółowe dane dotyczące wydajności procesora „Venice” czy dokładnej daty premiery nie zostały podane, ale firma podkreśla, że prace nad projektem przebiegają zgodnie z harmonogramem, a w przyszłym roku gotowy, 2-nanometrowy chip „Venice” powinien trafić do pierwszych odbiorców. Dlaczego ta informacja ma znaczenie? Układy HPC stanowią trzon wielu centrów danych, to one odpowiadają za rozproszone usługi cyfrowe i chmury danych, a także coraz dynamiczniej rozwijającą się sztuczną inteligencję. Fakt, że udało się zaprojektować i wykonać (przekazanie do produkcji oznacza wykonalność projektu) oznacza, że przyszłe centra danych uzyskają wyższą wydajność przy jednocześnie niższym poborze mocy, co w epoce wymagającej koncentracji na tym, gdzie i w jaki sposób zużywamy energię, nie jest bez znaczenia.

Jeśli artykuł AMD już korzysta z 2-nanometrowej technologii – to pierwszy przypadek w klasie chipów HPC nie wygląda prawidłowo w Twoim czytniku RSS, to zobacz go na iMagazine.

![[09.05.2025] Szkolenie on-line: Estoński CIT - zasady, korzyści oraz pułapki](https://www.podatki.biz/layoutv4/images/min2-logo_edukacja_biale.png)

![Paulina Hennig-Kloska w programie "Gość Wydarzeń" [OGLĄDAJ]](https://redirector.redefine.pl/cp/22u1daxhndzkzsufgb4b2ammtgryr4rr.png?#)

![Jak Polacy planowali świąteczne wydatki? Ilu było gotowych zadłużyć się, byle w Wielkanoc móc "jeść, pić i popuszczać pasa"? [BADANIE]](https://static.wiadomoscihandlowe.pl/images/2025/04/22/581106.webp?#)

![Kadra Realu Madryt na mecz przeciwko Getafe. Wiadomo, co z Kylianem Mbappé [OFICJALNIE]](https://transfery.info/img/photos/103686/1500xauto/real-madryt.jpg)